作成:Fukushima

なぜFPGAなのか

CPUを使用したソフトウェアに対しては演算速度で有利である。特定用途向けのLSIであるASICに対しては費用面で有利である。なお、ASICはFPGAと同様にハードウェアである。

以下に、ソフトウェア、ASICそれぞれに対する優位点をあげる。

【ソフトウェアに対する優位点】

ソフトウェアはCPUで実行される。一般的にソフトウェアは逐次処理であるため、forループなどで繰り返し処理の回数が多くなると演算に長い時間がかかる。また同様に逐次処理であるため、データ入力後に演算が終了して結果を出力するまでは新しいデータを入力することができない。つまり、データ量が多くなると演算完了までの時間が長くなる。

FPGAは演算の並列実行が可能である。繰り返し処理に関しては、ループを展開して並列に演算することで全体の処理時間を短縮できる。CPUがデータを次々に入力できない点に関しては、FPGAではデータを連続して入力し結果が順次出力されるように回路を設計することで解決できる。このように次々と演算する仕組みをパイプラインという。FPGA回路設計ではパイプライン動作させるのが基本である。

【ACISに対する優位点】

ASIC(エーシック)とは特定用途向け集積回路のことである。ASICは一般的にFPGAよりも動作速度や消費電力、部品単価の点で優れている。一方で、開発費が高く開発期間も長い。また、一度製作すると回路の変更が困難である。

FPGAは回路の変更が可能なため設計時の誤りを後から修正することができる。これは設計および検証時間の短縮につながる。

回路変更ができるため、必要に応じて機能追加が可能である。ASICは製造工程にも時間がかかり納期が長いが、FPGAへのコンフィギュレーションデータの書き込みは長くても数分で完了する。

価格面では、大量に使用する場合はASICが有利だが、使用個数が少ない場合は開発イニシャル費が不要なFPGAのほうが費用を抑えることができる。

成果

- ソフトウェアと同等の処理(MRFの推論計算)をFPGAで実装できた

- ソフトウェアでループの繰り返し回数が多い処理をFPGAで高速に実行できた

- FPGAでの演算は処理時間にばらつきがなく既知の時間で実行が完了することを確認した

以下に詳細を述べる。

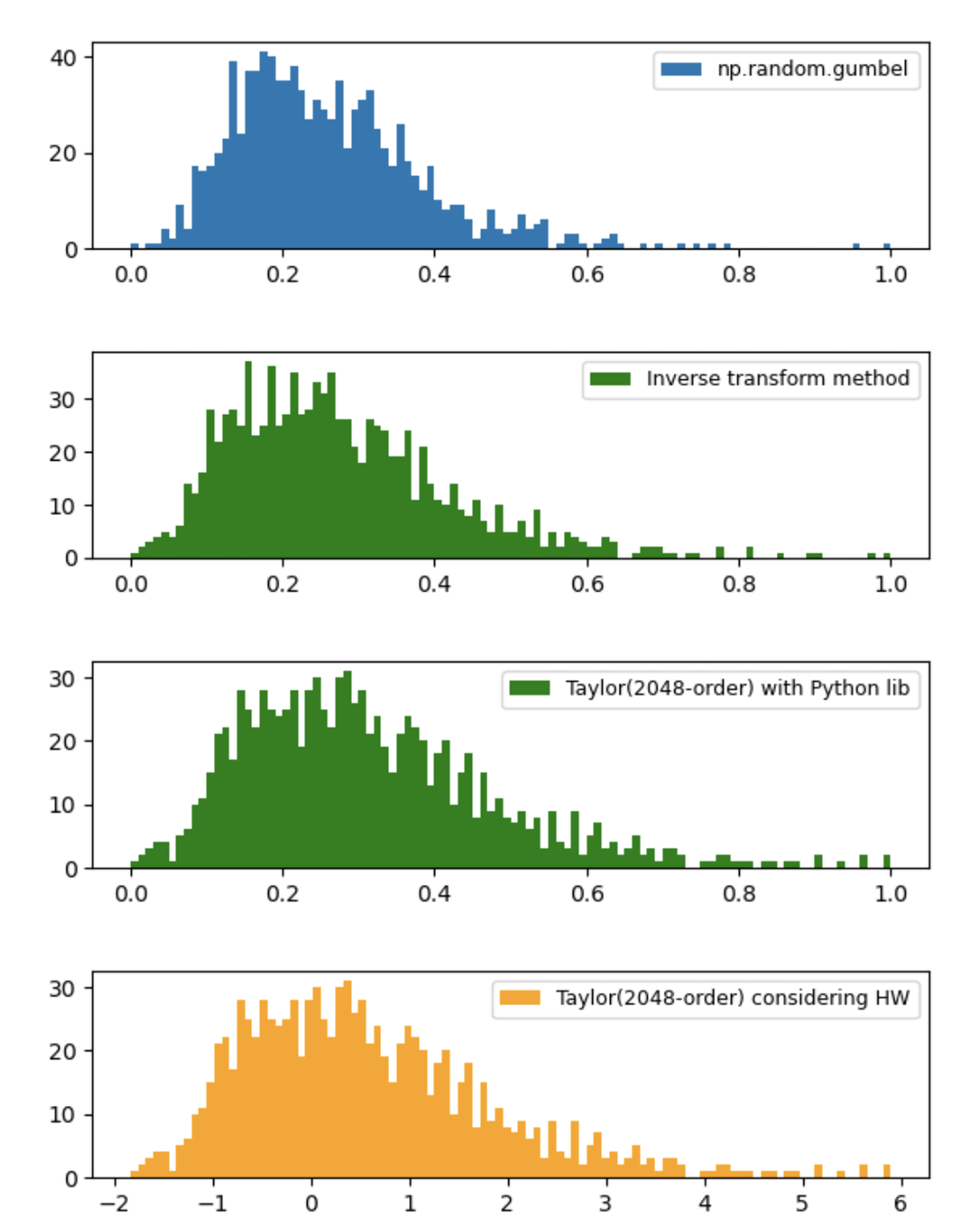

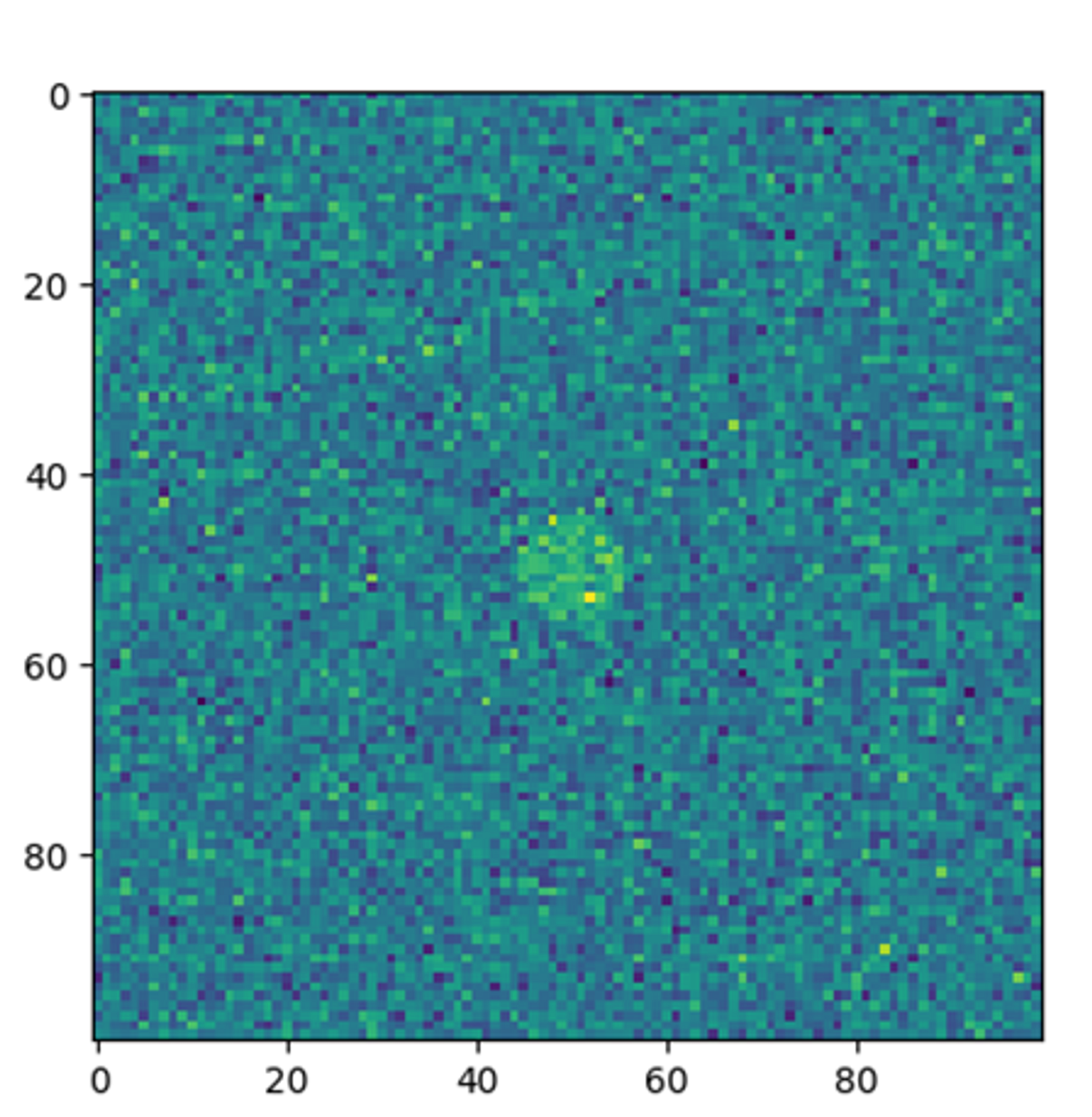

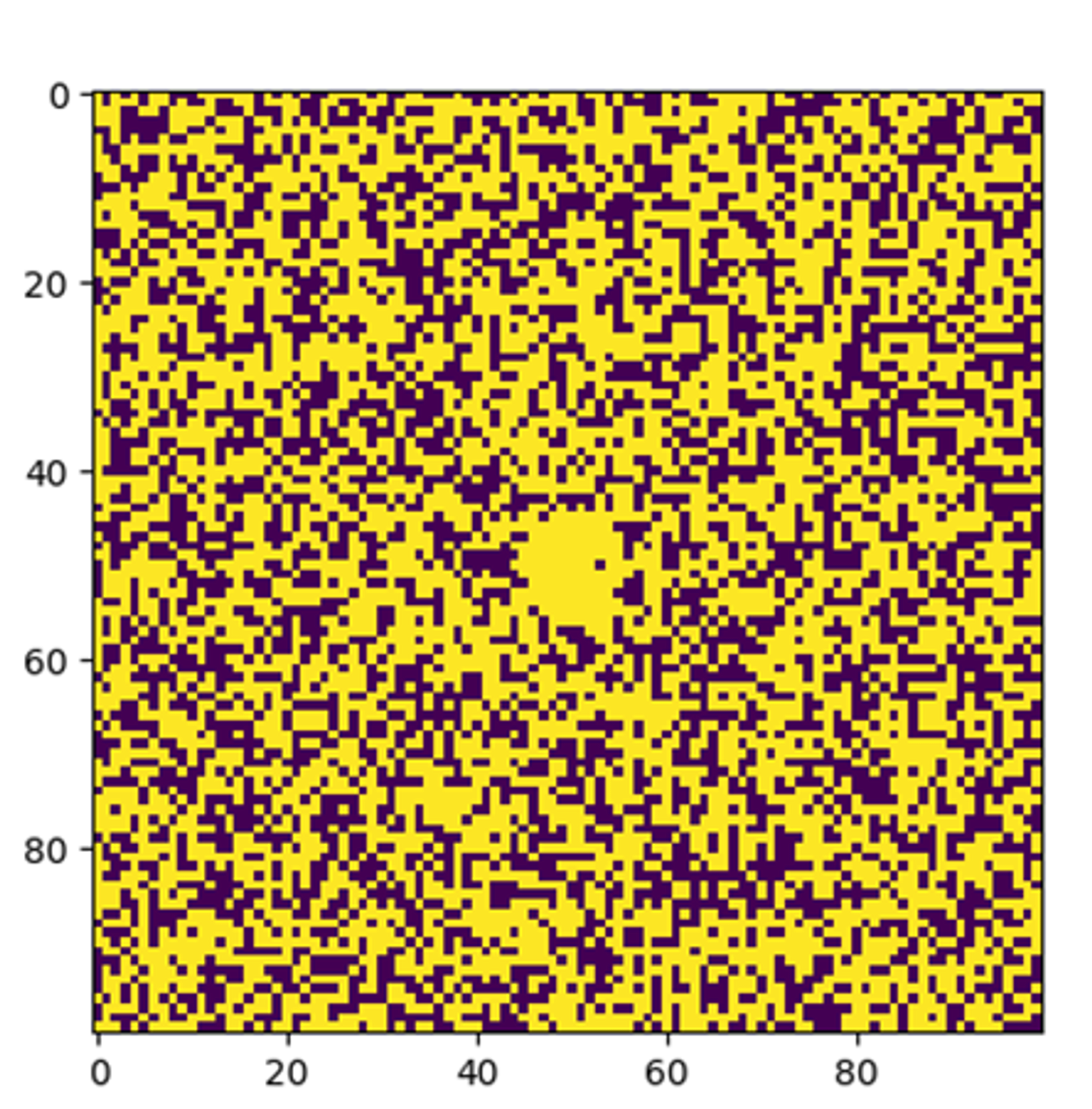

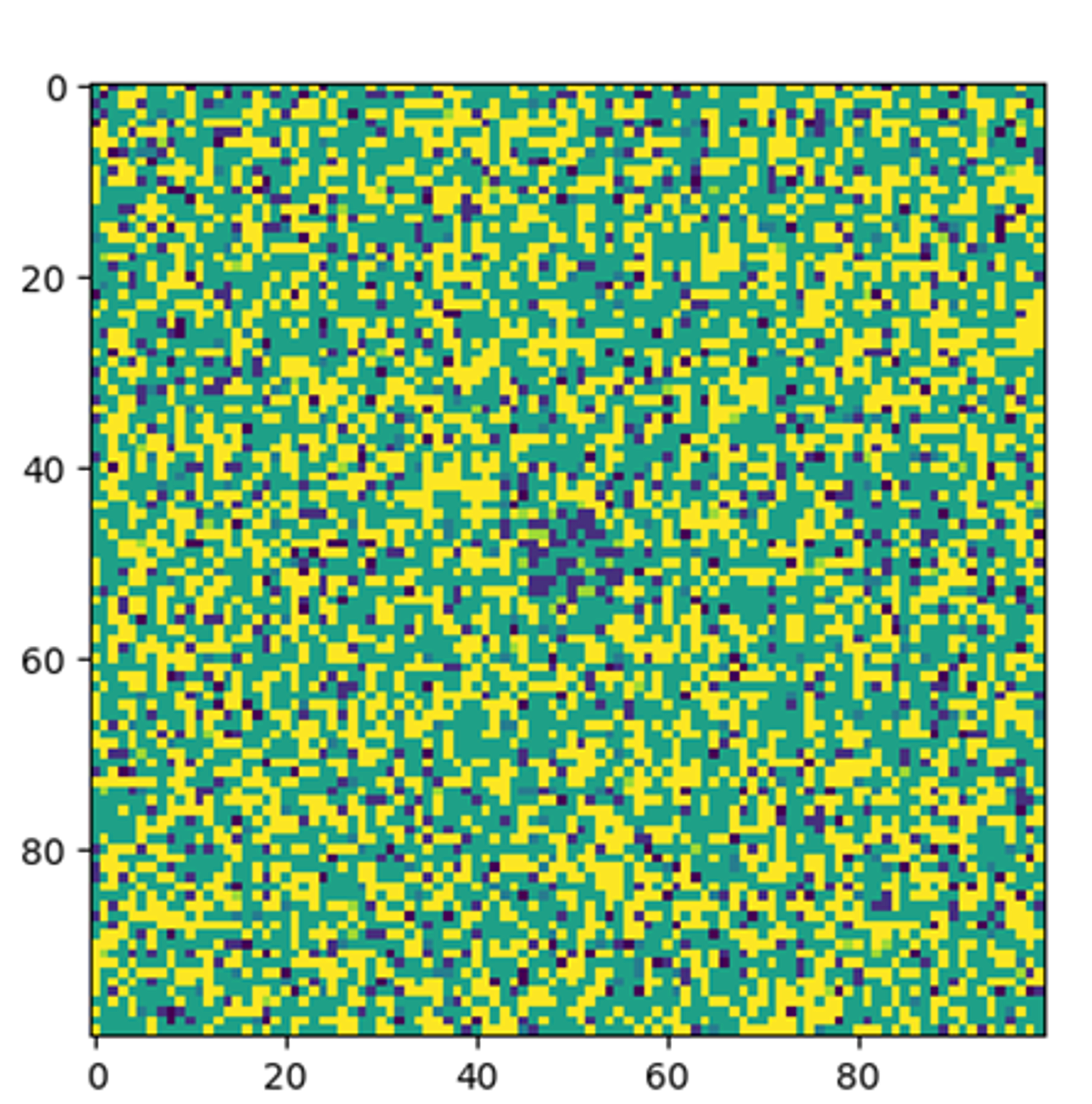

ノイズを付加した人工画像に対してギブスサンプリングを行い、ソフトウェア(PC上のPython)による演算結果とFPGAでの演算結果が同等であることを確認した。

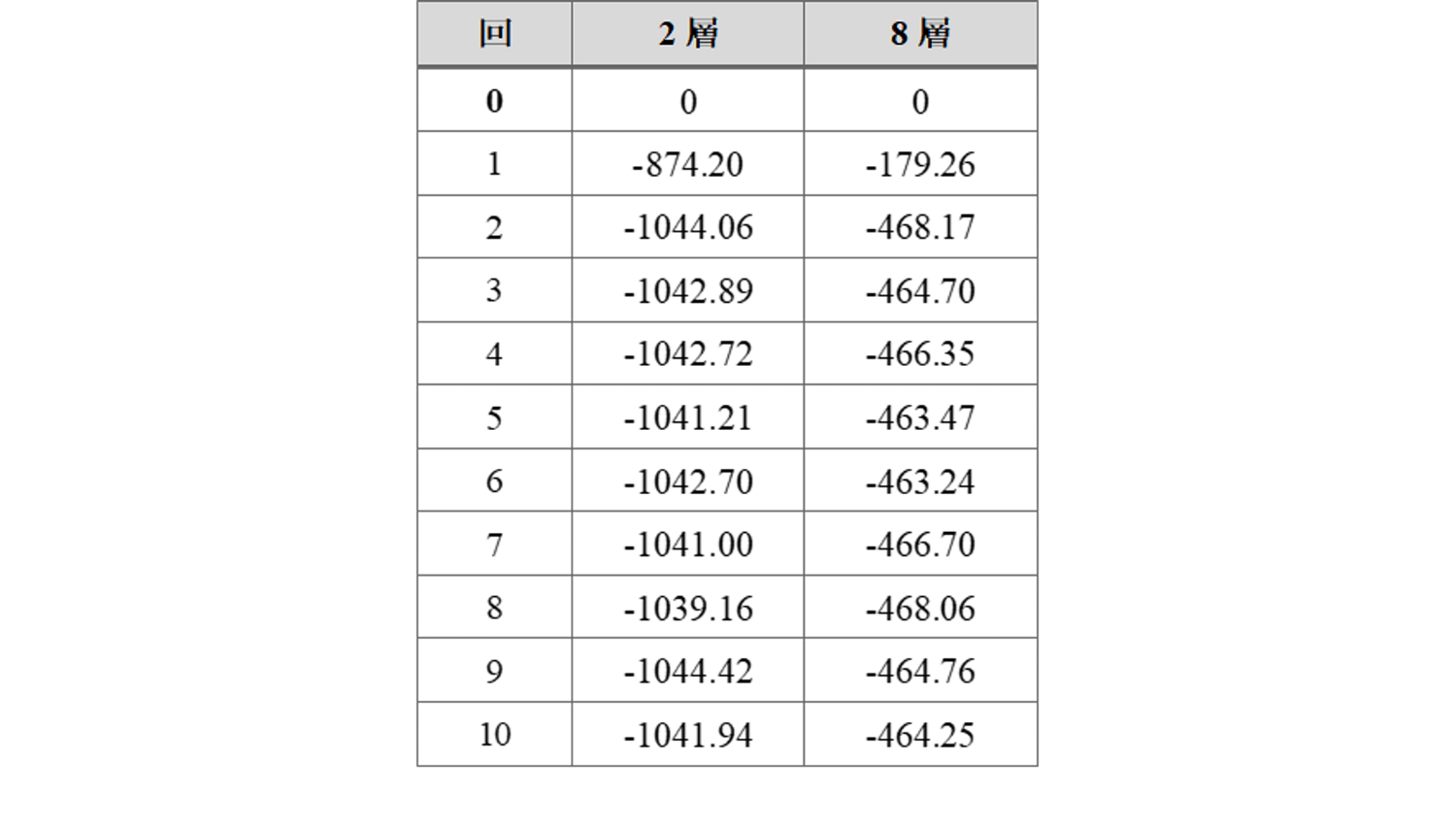

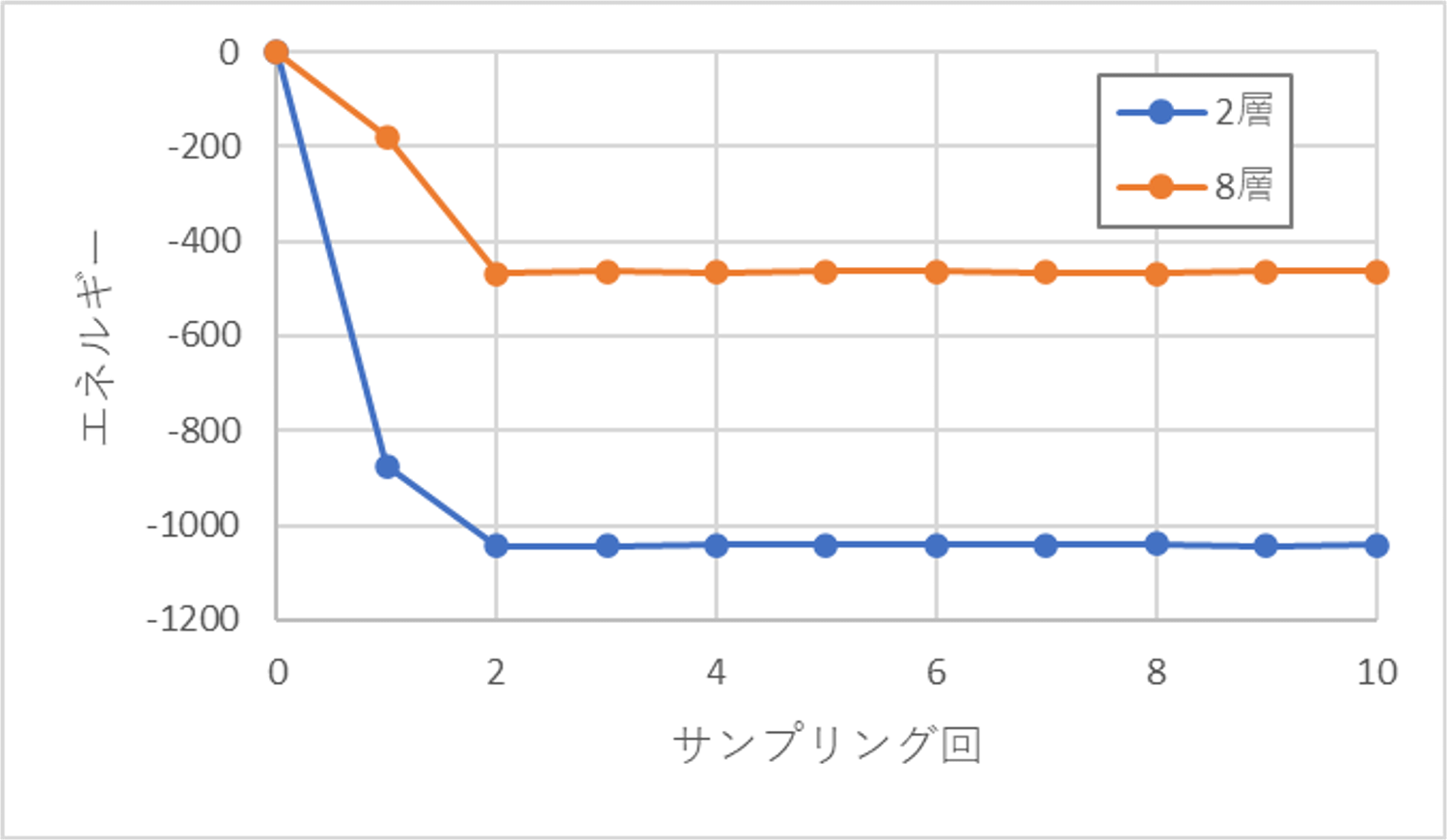

FPGAで演算の演算時、サンプリングを1回実行するごとに面内のMRFモデルの総エネルギーが減少していることを確認した。途中からは飽和している。

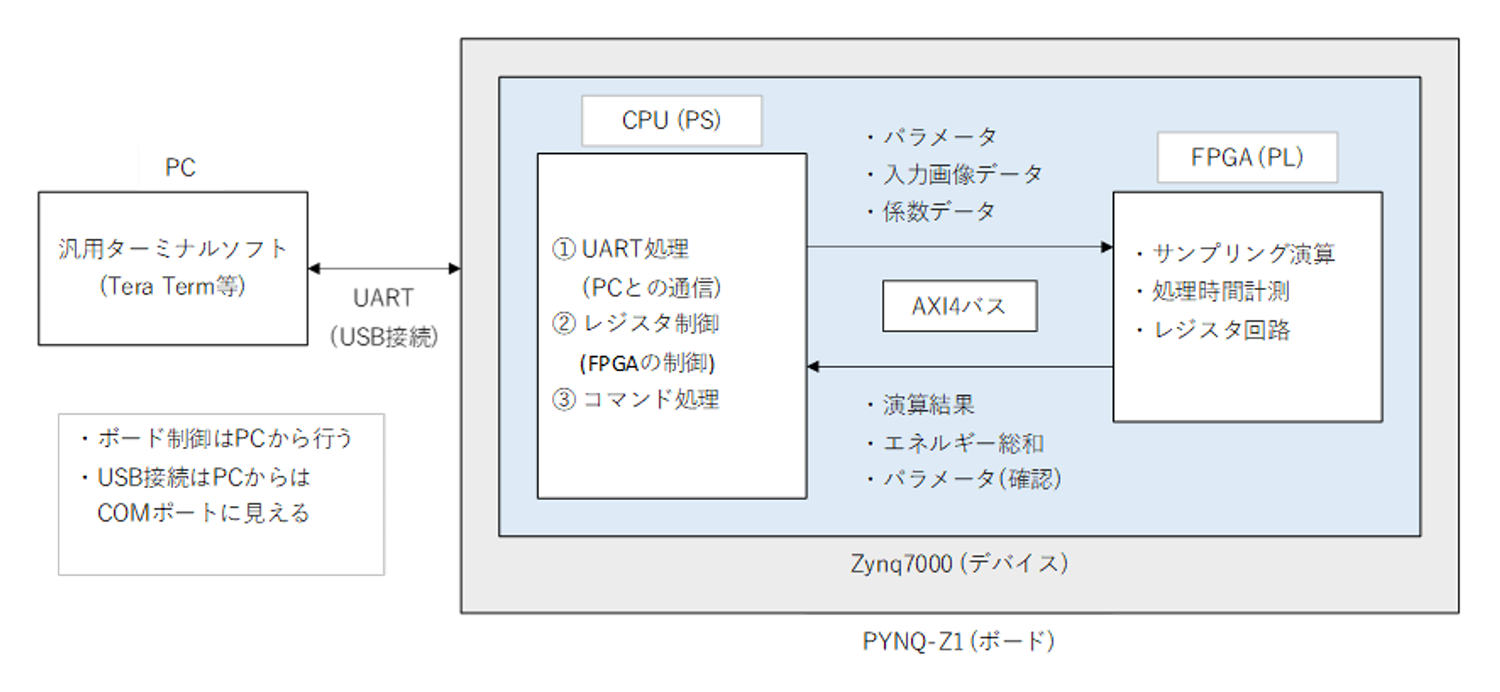

FPGAでの演算時間が設計値とほぼ等しいことを確認した。組み込みCPUからの開始指示等でオーバーヘッドが発生するため厳密には一致しない。

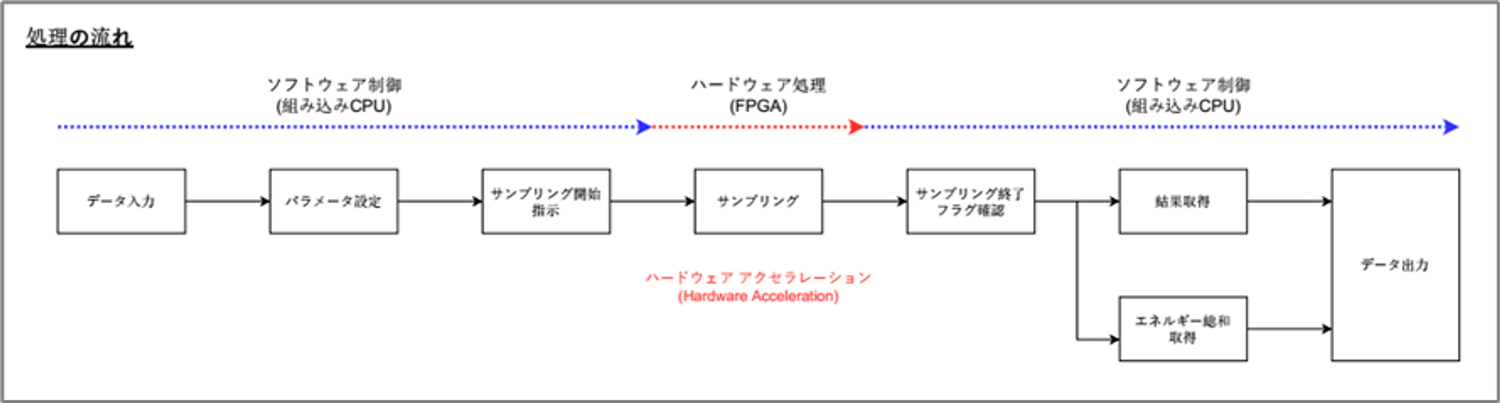

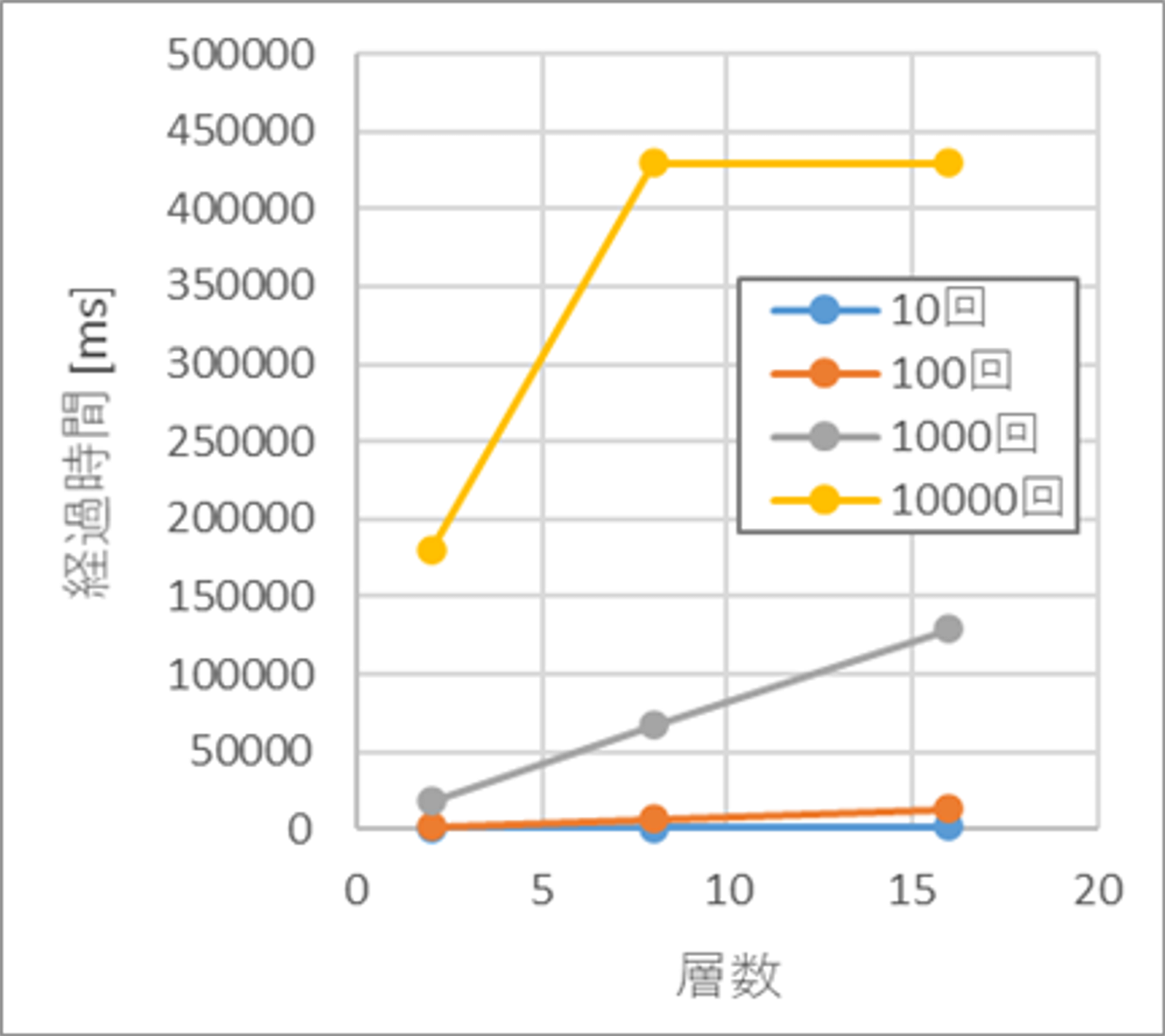

さらに、FPGAと組み込みCPUでの演算時間を比較した。下記に記述する「層数」「サンプリング回数」はパラメータであり、ソフトウェアではそれぞれforループでの繰り返し回数が変化するような実装である。

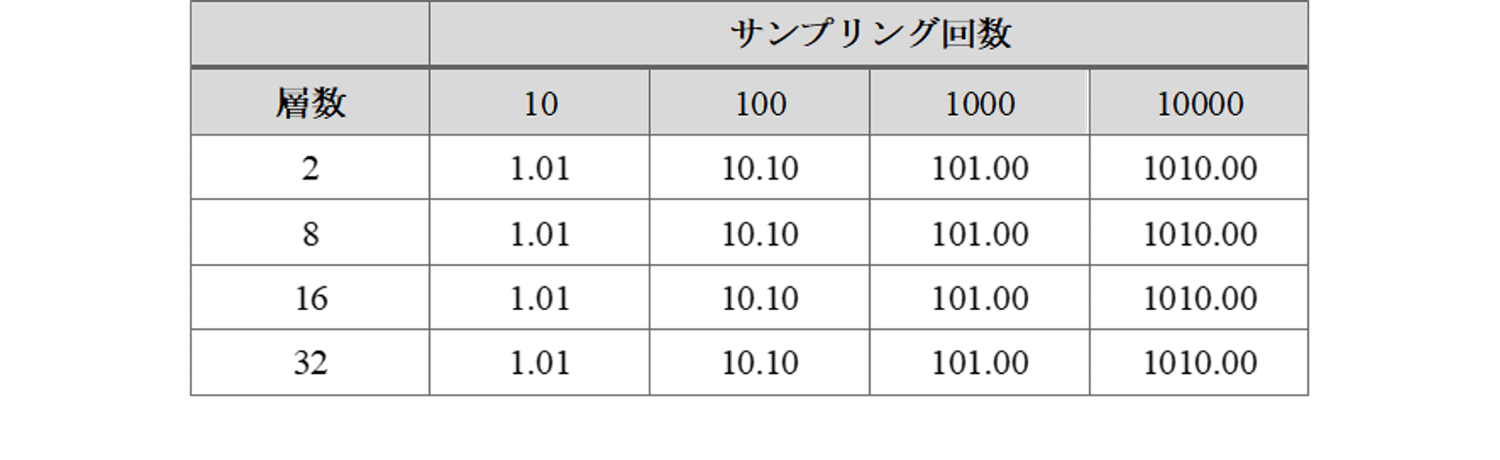

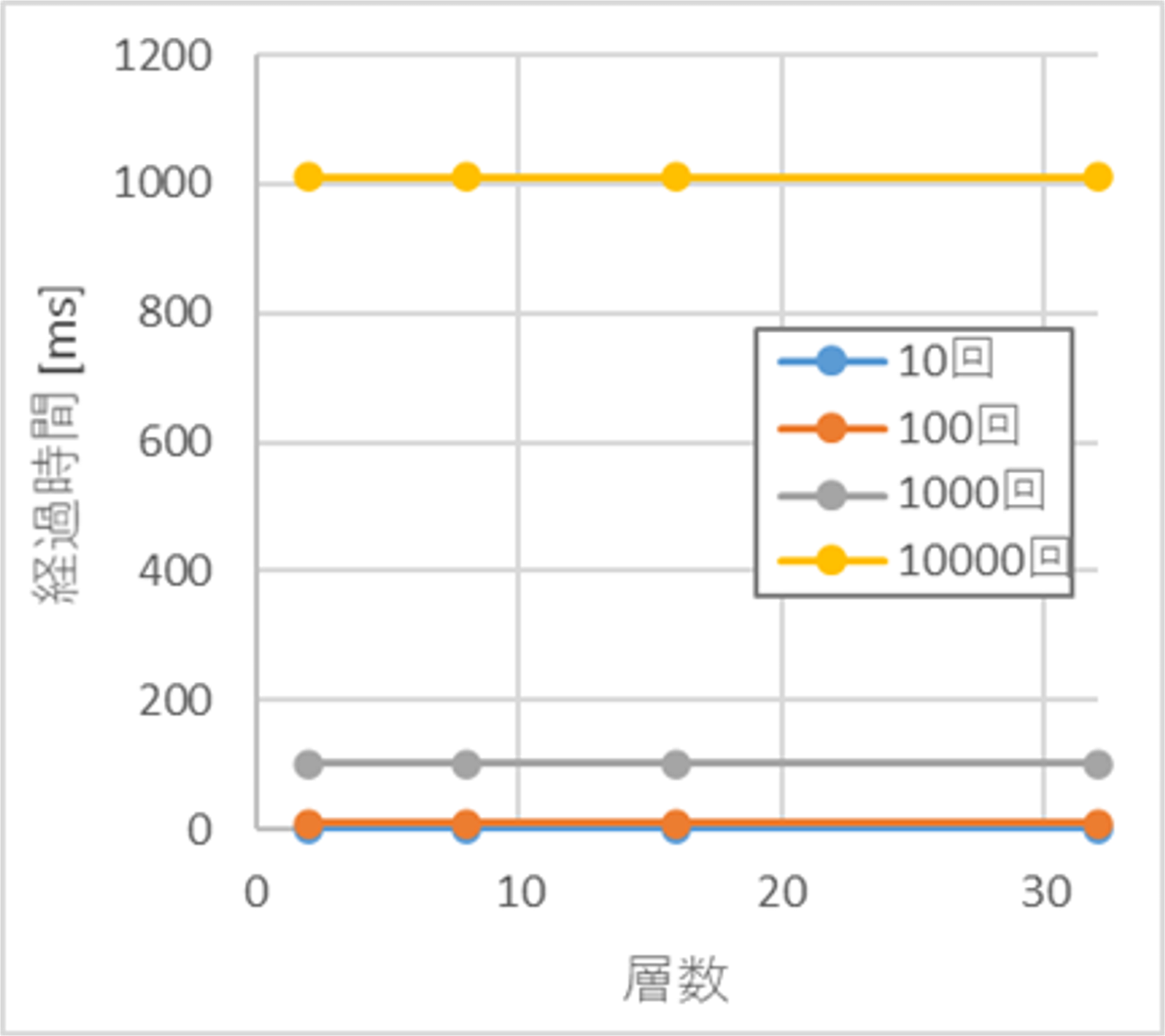

- FPGAでは層数の違いによる演算時間の差はない

- FPGAではサンプリング回数に正確に比例して演算時間が増加する

- FPGAでは複数回計測を繰り返しても演算時間にばらつきがない (演算時間は既知)

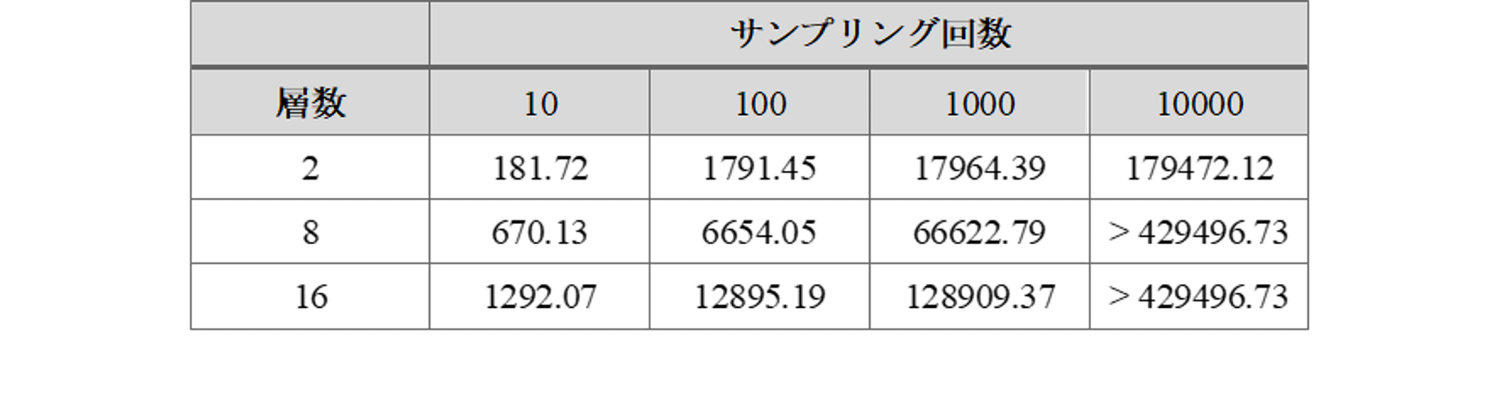

- 組み込みCPUでは層数に比例して演算時間が増加する

- 組み込みCPUではサンプリング回数に比例して演算時間が増加する

- 組み込みCPUでは複数回計測時に演算時間にばらつきが発生する

FPGAによるサンプリング実行時の経過時間(ms) (100×100画素)

組み込みCPUによるサンプリング実行時の経過時間(ms) (100×100画素)

(サンプリング回数10000回かつ層数8および16は計測用カウンタがオーバーフローした)

株式会社スクラムサイン

お問い合わせ

・お仕事のご依頼に関するお問い合わせ

・協業に関するお問い合わせ

・取材に関するお問い合わせ

・採用に関するお問い合わせ

・弊社へのご提案に関するお問い合わせ

下記のフォームよりよろしくお願いします。

情報セキュリティ基本方針

All rights reserved ScrumSign, Inc.